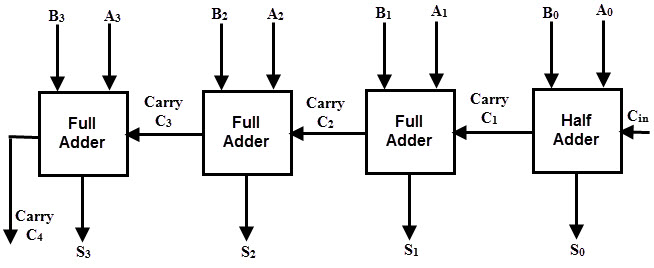

I want to compare performance of 4-bit full adder vs sequantial (serial ) adder with one D flip flop .. The two models are in the followig figures

Combinational adder:

Serial adder:

Lets say in gate level AND, OR and NOT gates will have time delay 30 ns, 20 ns and 10 ns, respectively. And the setup and hold time for D-flipflop are 10 ns and 5 ns, respectively. The problem is I am not sure how to compute the delay, or how to deal with the path that I should select. I have seen some videos in youtube and they were not helpful.

Can anyone please show me the way cause I want to make use of it .. Thanks in advance

No comments:

Post a Comment